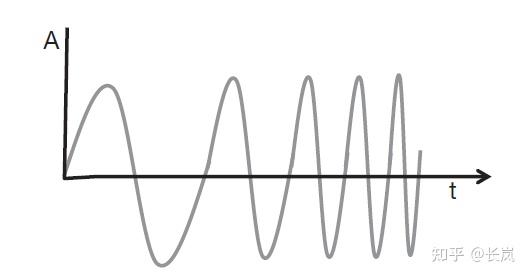

锁相环输出频率的相位与参考时钟的相位是否为同相

锁相环(PLL)的输出频率的相位和参考时钟的相位不一定是同相的,它们之间可能存在相位差。这是因为在PLL中,参考时钟和输出频率信号都是经过频率除法器处理的信号,而频率除法器会对信号的相位产生影响。

具体来说,在PLL中,参考时钟通过一个相位检测器与反馈信号进行比较,以产生控制电压来调整VCO的频率。如果两个信号的相位有差异,那么相位检测器将产生一个误差电压来控制VCO的相位,使其与参考时钟的相位保持一致。但由于频率除法器的存在,输出频率信号的相位可能与参考时钟的相位存在一定的相位差。

因此,如果要确保输出频率的相位与参考时钟的相位保持一致,需要在PLL中加入相位校正电路。这种电路可以对输出频率信号进行相位校正,以消除由于频率除法器带来的相位差。但是,相位校正电路的设计比较复杂,需要根据具体情况进行综合考虑和优化。

版权声明:本文由射频1988发布,如需转载请注明出处,本人微信号:maoduntage,手机号:18513199638,淘宝店铺名字:射频1988,淘宝店铺地址:https://mcurf.taobao.com 如有业务需要请联系我即可,感谢各位老板。