锁相环芯片的参考时钟幅值过大会导致啥问题出现以及出现的原因是啥

锁相环(PLL)芯片的参考时钟幅值过大可能会导致以下问题:

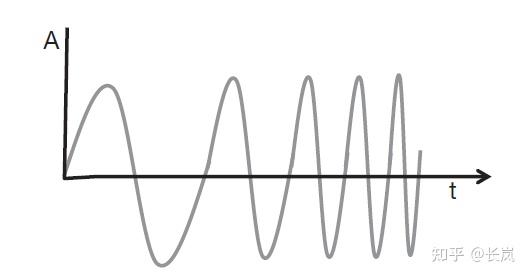

振荡器非线性失真:参考时钟幅值过大可能引起振荡器非线性失真,导致输出的时钟信号含有高次谐波成分。这会导致时钟信号的频谱不纯净,并且可能引入额外的噪声。

相位偏差增加:PLL的作用就是将输入参考时钟的相位与输出时钟的相位同步。当参考时钟幅值过大时,PLL可能无法正确跟踪参考时钟的相位,导致输出时钟相位的偏差增加。

锁定时间延长:参考时钟幅值过大可能会增加PLL系统的稳定性要求,导致锁定时间延长。PLL需要更长的时间来达到准确的相位和频率锁定,从而影响系统的响应速度和性能。

产生该问题的原因可能有以下几点:

参考时钟源的问题:如果参考时钟源本身存在幅值过大的问题,那么进入PLL的参考时钟信号也会具有较大的幅值。

PLL参数设置错误:在设计和配置PLL时,如果参数设置不当,比如放大倍数过大或环路滤波器参数不合适,也可能导致参考时钟幅值过大。

环路滤波器失效:环路滤波器的作用是平滑PLL系统中的错误信号,并控制输出频率和相位的稳定性。如果滤波器失效或工作不正常,就有可能导致参考时钟幅值过大。

在设计和使用锁相环芯片时,需要注意选择合适的参考时钟幅值,并确保PLL系统的各个部分都正确配置和工作,以避免上述问题的出现。

版权声明:本文由射频1988发布,如需转载请注明出处,本人微信号:maoduntage,手机号:18513199638,淘宝店铺名字:射频1988,淘宝店铺地址:https://mcurf.taobao.com 如有业务需要请联系我即可,感谢各位老板。